Imballaggio dei semiconduttori gioca un ruolo cruciale nell’elettronica moderna, fungere da ponte tra i circuiti integrati (circuiti integrati) e componenti esterni. Non solo protegge i delicati chip dei semiconduttori, ma garantisce anche collegamenti elettrici e gestione termica efficienti. Man mano che i dispositivi elettronici diventano più compatti e potenti, soluzioni di packaging avanzate sono essenziali per supportare il calcolo ad alte prestazioni, dispositivi mobili, e applicazioni automobilistiche.

Confezione multi-chip (MCP) è emersa come una tecnologia chiave per migliorare l'integrazione consentendo di alloggiare più matrici di semiconduttori all'interno di un unico pacchetto. Questo approccio migliora le prestazioni, riduce il consumo energetico, e ottimizza l'utilizzo dello spazio, rendendolo ideale per applicazioni che richiedono integrazione ad alta densità.

UN Leadframe multichip è una componente fondamentale di MCP, fornendo la struttura strutturale e i percorsi elettrici necessari per l’interconnessione di più chip. La sua importanza risiede nell'offrire una soluzione di imballaggio economicamente vantaggiosa e termicamente efficiente, rendendolo ampiamente utilizzato nell'elettronica di consumo, sistemi automobilistici, e dispositivi di comunicazione.

Cos'è un leadframe multi-chip?

Nella confezione dei semiconduttori, un leadframe è una struttura metallica che fornisce supporto meccanico e collegamenti elettrici per un circuito integrato (CIRCUITO INTEGRATO). Funziona come un ponte tra il die del semiconduttore e il circuito esterno, garantendo la trasmissione del segnale e la dissipazione termica. I leadframe sono ampiamente utilizzati nel tradizionale confezionamento di circuiti integrati grazie al loro rapporto costo-efficacia, ottima conduttività, e affidabilità nella produzione di massa.

UN Leadframe multichip differisce da un leadframe a chip singolo poiché consente di montare più matrici di semiconduttori sullo stesso framework. Mentre i leadframe a chip singolo supportano solo un die, limitare la funzionalità a una singola unità di elaborazione, i leadframe multi-chip integrano più chip in un unico pacchetto. Ciò consente funzionalità più elevate, consumo energetico ridotto, e una migliore efficienza del sistema senza aumentare l'ingombro fisico.

Funzionalmente, un leadframe multichip migliora le prestazioni del dispositivo riducendo al minimo i ritardi del segnale tra chip, migliorare la gestione termica, e riducendo i costi complessivi di imballaggio. Supporta applicazioni che richiedono un'elevata integrazione, come i processori mobili, controllori automobilistici, e moduli di comunicazione RF, rendendolo un componente cruciale nella moderna progettazione dei semiconduttori.

Componenti di un leadframe multi-chip

Un leadframe multichip è costituito da diversi componenti chiave che lavorano insieme per fornire supporto meccanico, connettività elettrica, e protezione ambientale per più stampi di semiconduttori. Questi componenti sono attentamente progettati per garantire prestazioni elevate, durabilità, ed efficiente integrazione nei moderni dispositivi elettronici.

Substrato metallico

Il substrato metallico è il fondamento strutturale di un leadframe multi-chip, fornendo stabilità meccanica e conduttività elettrica. I materiali comuni utilizzati includono:

- Rame (Cu): Il materiale più utilizzato grazie alla sua eccellente conduttività elettrica, dissipazione termica, e resistenza meccanica.

- Leghe di rame: Potenziato con elementi come ferro o nichel per migliorare la durezza e la resistenza all'ossidazione.

- Lega 42 (Lega di nichel-ferro): Offre una bassa dilatazione termica, rendendolo adatto ad applicazioni che richiedono elevata stabilità dimensionale.

La scelta del materiale dipende dai requisiti specifici del pacchetto di semiconduttori, come la dissipazione del calore, prestazioni elettriche, e costo di produzione.

Conduce

I conduttori sono i percorsi elettrici che collegano le matrici dei semiconduttori ai circuiti esterni. In un leadframe multi-chip, gli elettrocateteri devono essere progettati per accogliere più matrici, garantendo una trasmissione efficiente del segnale e riducendo al minimo la resistenza elettrica. Gli aspetti chiave della progettazione dei lead includono:

- Passo principale: La spaziatura tra i conduttori deve essere ottimizzata per l'integrazione ad alta densità evitando al contempo l'interferenza del segnale.

- Placcatura: I cavi sono spesso placcati con materiali come l'argento, oro, o palladio per migliorare la conduttività e proteggere dalla corrosione.

- Formare & Taglio: Dopo il processo di confezionamento, i cavi vengono tagliati e piegati per creare terminali esterni da saldare su circuiti stampati (PCB).

Tamponi di legame & Interconnessioni

I bond pad fungono da punti di connessione in cui le matrici dei semiconduttori si interfacciano con il leadframe. In un leadframe multi-chip, una progettazione efficiente delle interconnessioni è fondamentale per garantire una corretta comunicazione tra più stampi. Esistono due metodi di interconnessione principali:

- Incollaggio di fili: Per collegare i cuscinetti di collegamento di ciascun die al telaio conduttore vengono utilizzati sottili fili d'oro o di rame. Questo metodo è economico e ampiamente utilizzato negli imballaggi convenzionali.

- Incollaggio Flip Chip: Invece di fili, Vengono utilizzati punti di saldatura o interconnessioni a micro-pilastro, consentendo al chip di essere collegato direttamente al leadframe. Questo approccio riduce i ritardi del segnale e migliora le prestazioni elettriche.

La disposizione dei bond pad e delle interconnessioni deve essere attentamente pianificata per ridurre al minimo le interferenze del segnale e ottimizzare la distribuzione della potenza.

Incapsulamento & Stampaggio

L'incapsulamento è il processo di chiusura del leadframe multichip e dei relativi stampi semiconduttori all'interno di un materiale protettivo per proteggerlo da fattori ambientali come l'umidità, polvere, e stress meccanico. I metodi di incapsulamento più comuni includono:

- Composto per stampaggio epossidico (EMC): Fornisce una forte protezione meccanica e un'eccellente stabilità termica.

- Stampaggio a trasferimento: Un metodo di produzione ad alto volume in cui la resina riscaldata viene iniettata per formare un guscio protettivo attorno al telaio.

- Incapsulamento globale: Un metodo localizzato in cui un rivestimento protettivo viene applicato solo sullo stampo e sull'area di incollaggio, tipicamente utilizzato in applicazioni specializzate.

Un corretto incapsulamento garantisce affidabilità a lungo termine prevenendo l'ossidazione, danno meccanico, e contaminazione che potrebbe compromettere la funzionalità del multi-chip leadframe.

Vantaggi dei leadframe multi-chip

Un leadframe multichip offre numerosi vantaggi che lo rendono una scelta essenziale per il packaging dei semiconduttori, soprattutto in applicazioni che richiedono un'elevata integrazione, efficienza dei costi, e un'eccellente gestione termica. Questi vantaggi sono particolarmente preziosi in settori come l’elettronica di consumo, sistemi automobilistici, e calcolo ad alte prestazioni.

Alta integrazione

Uno dei principali vantaggi di un leadframe multichip è la sua capacità di integrare più die di semiconduttori all'interno di un unico package. Questo elevato livello di integrazione offre numerosi vantaggi:

- Spazio ridotto sul PCB: Ospitando più chip in un unico pacchetto, l'ingombro complessivo sul circuito stampato (PCB) è notevolmente ridotto. Questo è fondamentale per i dispositivi elettronici compatti come gli smartphone, indossabili, e applicazioni IoT.

- Prestazioni del sistema migliorate: L'integrazione multi-chip riduce la distanza tra i componenti funzionali, riducendo al minimo i ritardi del segnale e migliorando la velocità di trasferimento dei dati.

- Progettazione di circuiti semplificata: Un minor numero di singoli componenti sul PCB significa un instradamento più semplice e un rischio ridotto di guasti di interconnessione.

Combinando più matrici in un unico leadframe, i produttori possono creare soluzioni altamente integrate che migliorano le prestazioni dei dispositivi riducendo al contempo la complessità complessiva del sistema.

Efficienza dei costi

Rispetto ad altre tecnologie di confezionamento avanzate, un leadframe multichip offre una soluzione più conveniente per i produttori di semiconduttori. I principali vantaggi in termini di costi includono:

- Costi dei materiali inferiori: L'imballaggio basato su leadframe utilizza in genere fogli di metallo stampati o incisi, che sono significativamente più economici dei pacchetti basati su substrati che richiedono processi di produzione complessi.

- Processo di produzione semplificato: A differenza degli imballaggi a livello di flip-chip o wafer, la produzione di leadframe non richiede costose vie di silicio passanti (TSV) o livelli di ridistribuzione (RDL), rendendolo più conveniente.

- Tassi di rendimento più elevati: Il processo di produzione del leadframe maturo e consolidato si traduce in meno difetti e rendimenti di produzione più elevati, ridurre gli sprechi e migliorare l’efficienza complessiva.

Questi vantaggi in termini di costi fanno Leadframe multi-chip un'opzione interessante per le applicazioni che richiedono prestazioni elevate senza incorrere nei costi elevati associati agli imballaggi avanzati basati su substrati.

Prestazioni termiche

La gestione termica è un fattore critico nel packaging dei semiconduttori, in particolare per applicazioni ad alta potenza. I leadframe multichip forniscono eccellenti prestazioni termiche grazie a:

- Dissipazione diretta del calore: Il telaio in metallo funge da diffusore di calore naturale, condurre in modo efficiente il calore lontano dalle matrici del semiconduttore.

- Gestione della potenza migliorata: Le configurazioni multi-chip spesso generano più calore, ma le strutture del leadframe consentono un efficace dissipazione del calore, garantendo prestazioni stabili in condizioni di carico elevato.

- Compatibilità con soluzioni di raffreddamento aggiuntive: I pacchetti leadframe possono essere integrati con dissipatori di calore, vie termiche, o anche sistemi di raffreddamento a liquido per una migliore dissipazione del calore in applicazioni impegnative come moduli di potenza automobilistici e processori per data center.

Offrendo un'efficiente dissipazione del calore, I leadframe multichip consentono ai chip ad alte prestazioni di funzionare in modo affidabile anche in caso di carichi di lavoro intensivi.

Flessibilità di progettazione

Un altro vantaggio significativo dei leadframe multichip è la loro adattabilità a diverse architetture di chip e configurazioni di package. Questa flessibilità consente ai produttori di personalizzare i progetti per applicazioni specifiche, tra cui:

- Supporto per varie dimensioni e funzioni di chip: Un leadframe multichip può ospitare die di dimensioni diverse, rendendolo adatto a sistemi complessi su chip (SoC) e integrazione eterogenea.

- Configurazioni di lead personalizzabili: I leadframe possono essere progettati con diversi conteggi e disposizioni di conduttori per soddisfare specifici requisiti elettrici e meccanici.

- Compatibilità con molteplici tecnologie di imballaggio: Leadframe multi-chip può essere utilizzato con il wire bonding, incollaggio flip-chip, e tecniche di legame ibrido, garantendo una maggiore versatilità progettuale.

Questo livello di flessibilità rende Leadframe multi-chip adatto per una vasta gamma di settori, compresa l'elettronica automobilistica, Moduli di comunicazione RF, e acceleratori IA.

Applicazioni di leadframe multichip

Il Multi-Chip Leadframe è ampiamente utilizzato in vari settori grazie alla sua capacità di integrare più matrici di semiconduttori all'interno di un unico pacchetto. Questa tecnologia migliora le prestazioni del dispositivo, riduce i costi di produzione, e ottimizza l'utilizzo dello spazio, rendendolo una soluzione ideale per applicazioni ad alta densità e ad alte prestazioni. Di seguito sono elencate le aree chiave in cui i leadframe multi-chip vengono ampiamente applicati.

Elettronica di consumo

La richiesta di compattezza, ad alte prestazioni, e dispositivi elettronici efficienti dal punto di vista energetico hanno guidato l'adozione di leadframe multi-chip nell'elettronica di consumo. Le applicazioni includono:

- Smartphone & Compresse: Questi dispositivi richiedono più componenti semiconduttori, compresi i processori, patatine di memoria, circuiti integrati di gestione dell'alimentazione, e moduli RF, per funzionare perfettamente in un fattore di forma ridotto. Un leadframe multichip consente un'integrazione efficiente di questi componenti, migliorare le prestazioni riducendo il consumo energetico.

- Dispositivi indossabili: Smartwatch, tracker di fitness, e realtà aumentata (AR) gli occhiali richiedono pacchetti di semiconduttori miniaturizzati ed efficienti dal punto di vista energetico. IL Leadframe multichip consente design compatti e leggeri mantenendo un'elevata capacità di elaborazione.

- Dispositivi IoT: Internet delle cose (IoT) applicazioni, come gadget per la casa intelligente e sensori industriali, traggono vantaggio dai leadframe multi-chip poiché combinano più funzioni, come la connettività wireless, gestione dell'energia, e sensori, in un unico pacchetto compatto, riducendo la complessità e i costi complessivi del dispositivo.

Le elevate capacità di integrazione dei leadframe multichip garantiscono che la moderna elettronica di consumo possa soddisfare la crescente domanda di prestazioni migliori, maggiore durata della batteria, e ingombro ridotto del dispositivo.

Elettronica automobilistica

L’industria automobilistica sta vivendo una rapida trasformazione con il progresso dei veicoli elettrici (Veicoli elettrici), guida autonoma, e sistemi di infotainment intelligenti. Leadframe multi-chip sono essenziali in diverse applicazioni automobilistiche critiche:

- Sistemi avanzati di assistenza alla guida (ADAS): Questi sistemi si basano su più chip per il radar, lidar, telecamere, ed elaborazione basata sull’intelligenza artificiale. Il Multi-Chip Leadframe aiuta a integrare questi componenti in modo efficiente, garantendo l'elaborazione dei dati ad alta velocità mantenendo un fattore di forma compatto.

- Centraline elettroniche (ECU): I veicoli moderni dispongono di più ECU che gestiscono funzioni come il controllo del motore, frenatura, sterzo, e trasmissione. Il Multi-Chip Leadframe migliora le prestazioni dell'ECU integrando più chip per l'elaborazione dei dati e il processo decisionale in tempo reale.

- Unità di gestione dell'energia (PMU): I veicoli elettrici e ibridi richiedono una gestione avanzata della potenza per ottimizzare l’utilizzo della batteria e il controllo del motore. Il Multi-Chip Leadframe aiuta a progettare moduli di potenza efficienti che garantiscono un'efficace conversione dell'energia e una gestione termica.

Con la crescente complessità dell’elettronica automobilistica, Leadframe multi-chip offrire una soluzione di imballaggio economicamente vantaggiosa e termicamente efficiente che garantisce affidabilità e longevità in ambienti difficili.

5G & Comunicazione

L’implementazione della tecnologia 5G e l’espansione delle reti di comunicazione ad alta velocità richiedono soluzioni avanzate di packaging di semiconduttori per gestire segnali ad alta frequenza ed elaborazione massiccia dei dati. Il Multi-Chip Leadframe è ampiamente utilizzato in:

- Moduli front-end RF (FEM RF): Questi moduli integrano più componenti RF, come gli amplificatori di potenza, amplificatori a basso rumore, e filtri, per consentire la comunicazione wireless ad alta velocità. IL Leadframe multichip aiuta a ridurre la perdita di segnale e a migliorare le prestazioni RF complessive.

- Processori in banda base: Responsabile dell'elaborazione dei segnali cellulari, i processori in banda base richiedono un'elevata potenza computazionale e un'efficiente dissipazione termica. Leadframe multi-chip garantiscono che questi processori funzionino alle massime prestazioni riducendo al minimo il consumo energetico.

- Infrastruttura di rete: 5Stazioni base G, router, e i processori di segnale si affidano a dispositivi a semiconduttore con capacità di elaborazione dati ad alta velocità. Leadframe multi-chip fornire una soluzione conveniente per l'integrazione di più unità di elaborazione e circuiti di gestione dell'alimentazione.

Mentre la tecnologia 5G continua ad evolversi, I leadframe multi-chip svolgono un ruolo cruciale nel garantire velocità, più affidabile, e una comunicazione wireless più efficiente

Calcolo ad alte prestazioni (HPC)

La domanda di calcolo ad alte prestazioni nell’intelligenza artificiale (AI), centri dati, e le apparecchiature di rete stanno determinando la necessità di soluzioni avanzate di packaging per semiconduttori. Leadframe multi-chip sono particolarmente utili in:

- Acceleratori IA: Le applicazioni AI richiedono hardware specializzato, come GPU e processori specifici per l'intelligenza artificiale, per gestire calcoli complessi. Leadframe multi-chip consentire l'integrazione di più unità di elaborazione, patatine di memoria, e circuiti di gestione dell'alimentazione in un unico pacchetto, migliorare l’efficienza della lavorazione.

- Centri dati: Il cloud computing e l'analisi dei big data dipendono da processori e moduli di memoria ad alte prestazioni. Leadframe multi-chip contribuire a ottimizzare la gestione termica e l'efficienza energetica, garantendo che i data center funzionino ad alte prestazioni senza eccessivo accumulo di calore.

- Chip di rete: Router, interruttori, e i dispositivi di edge computing richiedono capacità di trasmissione ed elaborazione rapida dei dati. Leadframe multi-chip migliorare questi chip integrando più unità di elaborazione e comunicazione in un pacchetto compatto, migliorare la velocità di trasferimento dei dati e ridurre la latenza.

Mentre l’intelligenza artificiale e il cloud computing continuano a crescere, Leadframe multi-chip rimarrà una tecnologia fondamentale per migliorare la potenza di elaborazione, riducendo il consumo energetico, e consentendo una gestione dei dati più efficiente.

Processo di produzione del leadframe multi-chip

IL Leadframe multichip il processo di produzione prevede più fasi, dalla fabbricazione della struttura del leadframe all'assemblaggio delle matrici dei semiconduttori e all'incapsulamento del pacchetto finale. Ogni passaggio è progettato per garantire un'elevata precisione, prestazioni elettriche, e durabilità per le moderne applicazioni dei semiconduttori. Di seguito è riportata una panoramica dettagliata dei principali processi coinvolti.

Fabbricazione del leadframe

La fondazione dell'a Leadframe multichip è la sua struttura metallica, che funge da supporto meccanico e interconnessione elettrica per più matrici di semiconduttori. Esistono due tecniche di fabbricazione principali:

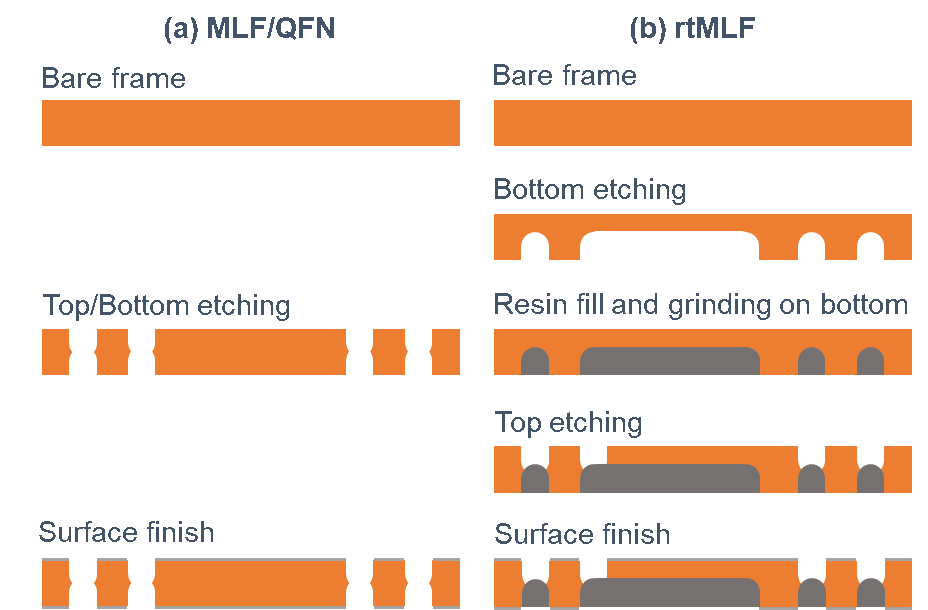

- Stampaggio: Questo processo ad alta velocità prevede l'utilizzo di una matrice di precisione per punzonare i leadframe da una striscia metallica continua. È ideale per la produzione di volumi elevati e offre una produzione economicamente vantaggiosa per progetti di leadframe standard.

- Acquaforte: Un processo di incisione chimica viene utilizzato per strutture leadframe più complesse. Fornisce geometrie più fini e una maggiore flessibilità di progettazione, consentendo complesse configurazioni multi-chip che lo stampaggio non può ottenere.

La scelta tra stampaggio e incisione dipende da fattori come la complessità del design, volume di produzione, e considerazioni sui costi.

Placcatura & Trattamento superficiale

Per migliorare le prestazioni e la longevità del Leadframe multichip, vengono applicati trattamenti superficiali e processi di placcatura:

- Argento (Ag) Placcatura: Migliora la conduttività elettrica e migliora l'affidabilità del collegamento dei cavi.

- Oro (Au) Placcatura: Utilizzato per applicazioni di fascia alta dove sono richieste resistenza alla corrosione e incollabilità superiori.

- Palladio (Pd) Rivestimento: Offre un'eccellente resistenza all'ossidazione ed elimina la necessità di sottostrati di nichel.

- Nichel (In) Placcatura: Fornisce resistenza strutturale e previene la migrazione del rame, garantendo stabilità a lungo termine.

Queste tecniche di placcatura assicurano che il Leadframe multichip mantiene ottime prestazioni elettriche, resistenza alla corrosione, e durabilità meccanica.

Processo di assemblaggio

Una volta che Leadframe multichip è fabbricato e trattato, i die dei semiconduttori sono montati e interconnessi. Il processo di assemblaggio prevede diversi passaggi critici:

- Morire Allega: Le matrici dei semiconduttori sono montate saldamente sul leadframe utilizzando adesivi specializzati o paste saldanti. Il corretto allineamento e adesione garantiscono prestazioni elettriche e termiche stabili.

- Incollaggio di fili: Sottili fili d'oro o di rame vengono utilizzati per collegare i cuscinetti di collegamento del die al telaio conduttore, abilitazione del segnale e della trasmissione di potenza. Questo è il metodo di interconnessione più comune per Leadframe multichip pacchetti.

- Integrazione Flip-Chip: Nei progetti avanzati, Al posto del wire bonding viene utilizzata la tecnologia flip-chip. Sulla matrice vengono applicati dei rilievi di saldatura, consentendo collegamenti elettrici diretti al Leadframe multichip, riducendo la resistenza e migliorando l'integrità del segnale.

Integrando più stampi all'interno dello stesso pacchetto, IL Leadframe multichip il processo di assemblaggio consente di compattare, soluzioni di semiconduttori ad alte prestazioni.

Incapsulamento & Test

Dopo l'assemblaggio, IL Leadframe multichip è sottoposto a incapsulamento e test rigorosi per garantire affidabilità a lungo termine.

- Incapsulamento: La confezione è racchiusa in un composto per stampaggio epossidico (EMC) per proteggere i semiconduttori muore dall'umidità, polvere, e stress meccanico. Lo stampaggio a trasferimento è comunemente utilizzato per la produzione di volumi elevati, mentre l'incapsulamento glob-top viene applicato in casi specializzati.

- Test elettrici: Ogni Leadframe multichip il pacchetto viene sottoposto a test funzionali e parametrici per verificare l'integrità del segnale, efficienza energetica, e prestazioni termiche.

- Test di affidabilità: I pacchetti sono sottoposti a stress test, compresi i cicli di temperatura, resistenza all'umidità, e shock meccanico, garantendo che soddisfino gli standard del settore automobilistico, elettronica di consumo, e applicazioni industriali.

Questi passaggi finali garantiscono che il Leadframe multichip mantiene prestazioni costanti in varie condizioni ambientali, rendendolo una scelta affidabile per applicazioni di semiconduttori ad alta integrazione.

TECNOLOGIA ALCANTA(SHENZHEN)CO.,LTD

TECNOLOGIA ALCANTA(SHENZHEN)CO.,LTD